在全球半导体产业竞相追逐算力极限、人工智能大模型对计算资源需求持续攀升的背景下,北京大学科研团队凭借一项突破性成果,为全球计算领域注入新的活力——他们成功研发出一款基于阻变存储器的新型模拟矩阵计算芯片,标志着中国在高端算力自主化道路上迈出关键一步。

这项由北京大学人工智能研究院孙仲研究员团队与集成电路学院联合完成的研究,近日以论文形式发表于国际权威期刊《Nature·Electronics》。论文提出的“模拟计算”范式,颠覆了传统数字计算依赖二进制“0”与“1”的底层逻辑,转而通过电压和电流的连续变化直接完成复杂运算,为解决冯·诺依曼架构“存储墙”问题提供了全新思路。

传统数字芯片的计算过程,本质上是无数次“0变1、1变0”的开关操作。数据需在存储器与处理器间频繁搬运,如同狭窄管道中的洪流,既消耗时间又浪费能量。而北大团队研发的模拟芯片,则让计算回归“本质”——数学中的“10”不再被拆解为二进制序列,而是直接表现为十伏的电流或流动的能量。这种“存算一体”的设计,使芯片在硬件层面实现了计算与存储的深度融合,彻底摆脱了“内存墙”的束缚。

实验室数据显示,该芯片在16×16矩阵的24位定点求逆任务中,相对误差仅10⁻⁷,精度达到行业领先水平。更令人惊叹的是其效率:完成相同计算量,顶级GPU需运行一整天,而这款模拟芯片仅需一分钟,能效比提升100倍,且几乎不产生热量。这意味着,未来训练AI大模型时,原本需要数百张GPU组成的算力农场,可能被一颗巴掌大小的模拟芯片替代。

技术的突破不仅在于“快”,更在于“巧”。研究团队创新性地将“低精度模拟求逆”与“高精度模拟矩阵-向量乘法”结合:前者通过快速逼近提供初始解,后者利用精确修正确保最终精度,二者协同实现24位定点计算。配合块矩阵协同算法,多个芯片可并行求解更大规模矩阵,展现了“新型信息器件+原创电路+经典算法”的协同设计之美。

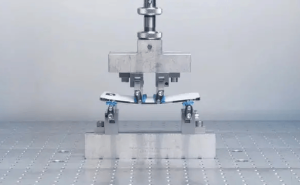

在硬件实现上,芯片采用40nm CMOS工艺,阻变存储器阵列支持3比特电导态编程。这种设计使计算与存储在物理层面合二为一,如同让思维与记忆回归同一脑区,使芯片能够“理解数据”而非简单“处理数据”。

实际应用中,这款芯片的表现同样惊艳。在大规模多输入多输出(MIMO)信号检测任务中,仅需三次迭代即可使接收图像与原始图像高度一致,误码率-信噪比曲线接近32位浮点GPU水平。这不仅为无线通信信号处理提供了加速方案,更可能成为AI训练中“二阶优化”的硬件基石,大幅降低模型训练成本。

对于边缘计算领域而言,这款芯片的低功耗、高精度特性更具革命性意义。未来,机器人、无人机、智能终端等设备将无需依赖云端,即可在本地完成AI模型的训练与推理,真正实现“端侧智能”。当AI能够直接在设备上学习、思考并决策,一个“万物智能”的时代将悄然来临。

孙仲研究员表示:“我们的目标不是取代GPU,而是与它形成互补,让计算更高效、更智慧。”这句话背后,既体现了科研工作者的务实态度,也彰显了中国在算力领域从追赶者到开辟者的自信。当电流开始“思考”,当“存算一体”成为现实,中国科学家正用创新与坚持,重新定义计算的边界。